NO.85-04

# S-3527

MSX System (MSX Port Controller and Software Controlled Sound Generator)

#### OUTLINE

YAMAHA S-3527 is an LSI developed for MSX computers. According to MSX specifications, it controls access to basic and expanded memories, VDP, keyboard, and peripheral devices like a printer. It incorporates SSG which is capable of generating music sound signals.

#### • FEATURES

- Access to ROM (MSX BASIC ROM: 32 Kbyte)

- Access to RAM (D-RAM: 16K-16 Kbyte or 64 Kbyte when expanded)

- Control of basic slots

- Selecting and controlling expansion slot

- Insertion of IWAIT during M1 cycle

- Access to keyboard (including numeric key pad)

- Incorporates two joysticks (or general ports)

- Incorporates SSG (equivalent of YAMAHA YM-2149)

Sound range: 8 octaves

Sound types: 3-channel square waves and 1-channel noise

Envelope control: 5 bits D/A converter : 5 bits

- CMOS device with Si gate

- Driven by +5V alone

- 100-pin plastic flat package

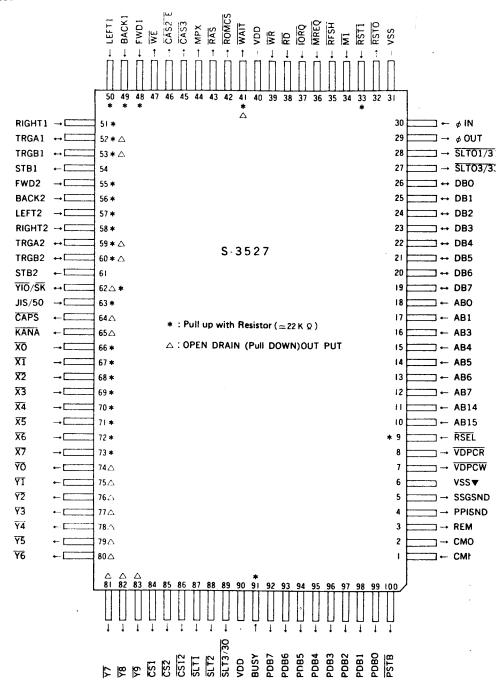

#### PIN ASSIGNMENT

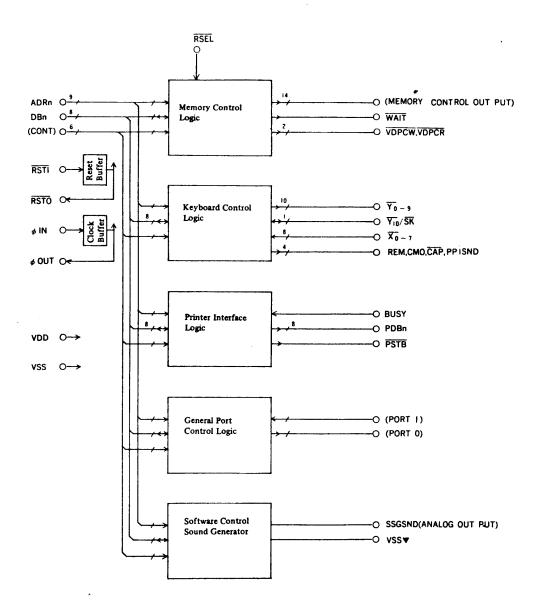

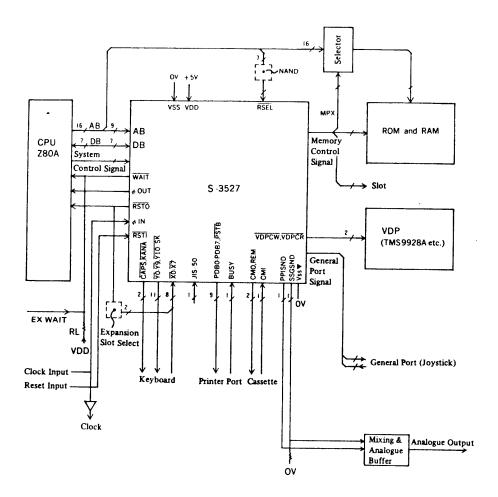

## ■ BLOCK DIAGRAM

(CONT): MI, RFSH, MREQ, TORQ, RD, WR

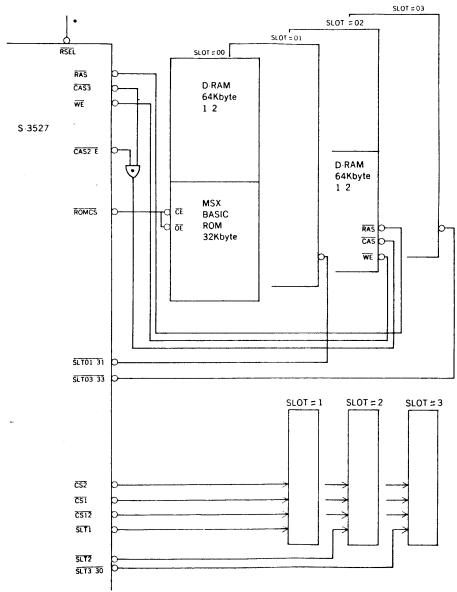

(MEMORY CONTROL OUT PUT): RONGS, RAS, MPX, CAS3, CAS2 E, WE, CS1, CS2, CS12, SLT1, SLT2, SLT3 30, SLT01 31, SLT03 33

(PORT I): FWD1, FWD2, BACK1, BACK2, LEFT1, LEFT2, RIGHT1, RIGHT2, (TRGA1, TRGA2, TRGB1, TRGB2) ( ): Wired Logic i/o (PORT O): (TRGA1, TRGB2, TRGB1, TRGB2) STB1, STB2

## PIN FUNCTIONS

| Pin Name                                  | I/O | Function                                                                                  |

|-------------------------------------------|-----|-------------------------------------------------------------------------------------------|

| ( AB15, AB14<br>( AB 7 ~ AB 3<br>AB1, AB0 | i   | Z80A CPU address bus in (9 bits)                                                          |

| DB 7 ~ DB0                                | i/o | Z80A CPU data bus in/out (8 bits)                                                         |

| Mī                                        | i   | Z80A CPU MI in                                                                            |

| RFSH                                      | i   | Z80A CPU RFSH in                                                                          |

| MREQ                                      | i   | Z80A CPU MREQ in                                                                          |

| IORQ                                      | i   | Z80A CPU TORQ in                                                                          |

| RD                                        | i   | Z80A CPU RD in                                                                            |

| ₩Ŕ                                        | i   | Z80A CPU WR in                                                                            |

| WAIT                                      | 0   | 1WAIT request signal out during M1 cycle (possible to wired-OR with external WAIT signal) |

| ROMCS                                     | 0   | MSX BASIC ROM select signal out                                                           |

| MPX                                       | 0   | D-RAM address multiplexing signal out                                                     |

| RAS                                       | 0   | D-RAM RAS signal out (RAS-only refresh possible by Z80)                                   |

| CAS2/E,CAS3                               | 0   | D-RAM CAS signal out {CAS3 : SLOT#0                                                       |

| WE                                        | o   | D-RAM WE signal out                                                                       |

| CS1,CS2,CS12                              | 0   | ROM select signal out (CS1: 4000-7FFF CS2: 8000-BFFF CS12: 4000-BFFF)                     |

| SLT1,SLT2,SLT3 30                         | 0   | Slot select signal out (SLT1: SLOT#1 SLT2: SLOT#2 SLT3 30: SLOT#3 or SLOT#30)             |

| SLT01.31                                  | 0   | Expansion slot # 01 or # 31 select signal out                                             |

| SLT03/33                                  | 0   | Expansion slot # 03 or # 33 select signal out                                             |

| RSEL                                      | i   | Expansion slot select register control signal in                                          |

| VDPCR                                     | 0   | VDP (video display processor) read timing signal out                                      |

| VDPCW                                     | 0 - | VDP write timing signal out                                                               |

| PDB7~PDB0                                 | 0   | Print data out (8 bits)                                                                   |

| PSTB                                      | o   | Printer strobe out                                                                        |

| when reset.)    Y9-Y0,(Y10/SK)   O(O/i)   Keyboard scan signal out (11 bits) (Y10 / SK receive serial key signal by selected function when reset.)    FWD1,FWD2   i   Joystick FWD signal or general port signal in                                                                                                                                                                                                                                                                                                                                                                                                                           | Pin Name                                                           | 1/0    | Function                                                                                                             |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------|

| when reset.)    Y9-Y0,(Y10/SK)   O(O/i)   Keyboard scan signal out (11 bits) (Y10 / SK receive serial key signal by selected function when reset.)    FWD1,FWD2   i   Joystick FWD signal or general port signal in                                                                                                                                                                                                                                                                                                                                                                                                                           | BUSY                                                               | i      | Printer status in                                                                                                    |

| selected function when reset.)  FWD1,FWD2  i Joystick FWD signal or general port signal in  BACK1,BACK2  i Joystick BACK signal or general port signal in  LEFT1,LEFT2  i Joystick LEFT signal or general port signal in  RIGHT1,RIGHT2  i Joystick RIGHT signal or general port signal in  TRGA1,TRGA2  i/o Joystick TRGA signal or general port signal out (I/O by wired logic)  TRGB1,TRGB2  i/o Joystick TRGB signal or general port signal out (I/O by wired logic)  STB1,STB2  o General port signal out  CMI  i Cassette tape read signal in  CMO  o Cassette tape write signal out  REM  o CAPS lamp signal out (drives LED directly) | <del>X7</del> ∼ <del>X0</del>                                      | i      | Keyboard return signal in (8 bits) ( $\overline{X6}$ and $\overline{X7}$ receive function select signal when reset.) |

| BACKI,BACK2  i Joystick BACK signal or general port signal in  LEFT1,LEFT2  i Joystick LEFT signal or general port signal in  RIGHT1,RIGHT2  i Joystick RIGHT signal or general port signal in  TRGA1,TRGA2  i/o Joystick TRGA signal or general port signal out (I/O by wired logic)  TRGB1,TRGB2  i/o Joystick TRGB signal or general port signal out (I/O by wired logic)  STB1,STB2  o General port signal out  CMI  i Cassette tape read signal in  CMO  o Cassette tape write signal out  REM  o Cassette tape control signal out  CAPS lamp signal out (drives LED directly)                                                           | $\overline{Y9} \sim \overline{Y0}, (\overline{Y10}/\overline{SK})$ | o(o/i) |                                                                                                                      |

| LEFT1,LEFT2  i Joystick LEFT signal or general port signal in  RIGHT1,RIGHT2  i Joystick RIGHT signal or general port signal in  TRGA1,TRGA2  i/o Joystick TRGA signal or general port signal out (I/O by wired logic)  TRGB1,TRGB2  i/o Joystick TRGB signal or general port signal out (I/O by wired logic)  STB1,STB2  o General port signal out  CMI  i Cassette tape read signal in  CMO  o Cassette tape write signal out  REM  o Cassette tape control signal out  CAPS  o CAPS lamp signal out (drives LED directly)                                                                                                                  | FWD1,FWD2                                                          | i      | Joystick FWD signal or general port signal in                                                                        |

| RIGHT1.RIGHT2 i Joystick RIGHT signal or general port signal in  TRGA1.TRGA2 i/o Joystick TRGA signal or general port signal out (I/O by wired logic)  TRGB1.TRGB2 i/o Joystick TRGB signal or general port signal out (I/O by wired logic)  STB1.STB2 o General port signal out  CMI i Cassette tape read signal in  CMO o Cassette tape write signal out  REM o Cassette tape control signal out  CAPS o CAPS lamp signal out (drives LED directly)                                                                                                                                                                                         | BACK1,BACK2                                                        | i      | Joystick BACK signal or general port signal in                                                                       |

| TRGA1,TRGA2  i/o  Joystick TRGA signal or general port signal out (I/O by wired logic)  TRGB1,TRGB2  i/o  Joystick TRGB signal or general port signal out (I/O by wired logic)  STB1,STB2  o  General port signal out  CMI  i  Cassette tape read signal in  CMO  o  Cassette tape write signal out  REM  o  Cassette tape control signal out  CAPS  o  CAPS lamp signal out (drives LED directly)                                                                                                                                                                                                                                            | LEFT1,LEFT2                                                        | i      | Joystick LEFT signal or general port signal in                                                                       |

| TRGB1,TRGB2 i/o Joystick TRGB signal or general port signal out (I/O by wired logic)  STB1,STB2 o General port signal out  CMI i Cassette tape read signal in  CMO o Cassette tape write signal out  REM o Cassette tape control signal out  CAPS o CAPS lamp signal out (drives LED directly)                                                                                                                                                                                                                                                                                                                                                | RIGHT1,RIGHT2                                                      | i      | Joystick RIGHT signal or general port signal in                                                                      |

| STB1,STB2  o General port signal out  CMI  i Cassette tape read signal in  CMO  o Cassette tape write signal out  REM  o Cassette tape control signal out  CAPS  o CAPS lamp signal out (drives LED directly)                                                                                                                                                                                                                                                                                                                                                                                                                                 | TRGA1,TRGA2                                                        | i/o    | Joystick TRGA signal or general port signal out (I/O by wired logic)                                                 |

| CMI i Cassette tape read signal in  CMO o Cassette tape write signal out  REM o Cassette tape control signal out  CAPS o CAPS lamp signal out (drives LED directly)                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | TRGB1,TRGB2                                                        | i/o    | Joystick TRGB signal or general port signal out (I/O by wired logic)                                                 |

| CMO  Cassette tape read signal in  CMO  Cassette tape write signal out  CAPS  CAPS lamp signal out (drives LED directly)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | STB1,STB2                                                          | 0      | General port signal out                                                                                              |

| CAPS o Cassette tape control signal out  CAPS lamp signal out (drives LED directly)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CMI                                                                | i      | Cassette tape read signal in                                                                                         |

| CAPS lamp signal out (drives LED directly)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | СМО                                                                | o      | Cassette tape write signal out                                                                                       |

| o Chi b tamp signar out (directly)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | REM                                                                | o      | Cassette tape control signal out                                                                                     |

| KANA (Kana lamp signal out (drives LED directly)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | CAPS                                                               | o      | CAPS lamp signal out (drives LED directly)                                                                           |

| C Rana ramp signal out (drives LED directly)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | KANA                                                               | o      | Kana lamp signal out (drives LED directly)                                                                           |

| JIS/50 i Keyboard arrangement control signal in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | JIS/50                                                             | i      | Keyboard arrangement control signal in                                                                               |

| RSTI i Reset signal in (input to Schmitt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RSTI                                                               | i      | Reset signal in (input to Schmitt)                                                                                   |

| RSTO o Reset signal out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | RSTÖ                                                               | 0      | Reset signal out                                                                                                     |

| PPISND o Software-defined sound out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PPISND                                                             | 0      | Software-defined sound out                                                                                           |

| SSGSND o SSG-generated analog sound out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SSGSND                                                             | 0      | SSG-generated analog sound out                                                                                       |

| ¢ IN Clock in (This is used via a buffer except for Z80A.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ø IN                                                               | i      | Clock in (This is used via a buffer except for Z80A.)                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ø OUT                                                              | o      | Clock for Z80A CPU out                                                                                               |

| VDD +5V power                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | VDD                                                                |        | +5V power                                                                                                            |

| vss ov gnd                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | vss .                                                              |        | ov gnd                                                                                                               |

| VSS▼. 0V SSG GND                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | vss▼                                                               |        | OV SSG GND                                                                                                           |

#### DESCRIPTION OF FUNCTIONS

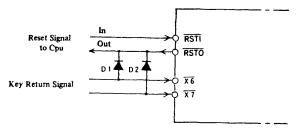

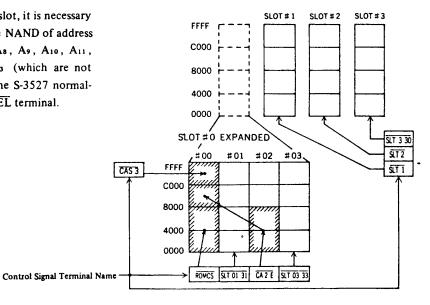

## > Selection of Function and Initialization

When the reset signal has come, it is possible to select an expansion slot and assign the numeric key drive signal output terminal  $(\overline{Y10} / \overline{SK})$  to receive serial keyboard signal, using  $\overline{X6}$  and  $\overline{X7}$  out of the keyboard return signal input terminals. As the sample circuit below shows, function is selected by the presence or absence of diodes  $D_1$  and  $D_2$  across the reset signal output terminal  $(\overline{RSTO})$  and the keyboard return signal input terminals. Memory maps shown on the next page indicate how expansion is realized.

$\overline{X6}$  and  $\overline{X7}$  input levels on initialization and functions

| <del>X</del> 6 | <u>X</u> 7 | Function                 | Diodes       |

|----------------|------------|--------------------------|--------------|

| 0              | X          | Slot 0 expansible        | D1 installed |

| 1              | ×          | Slot 3 expansible        | D1 removed   |

| X              | 0          | Serial key circuit works | D2 installed |

| X              | 1          | Numeric key driver works | D2 removed   |

#### Function select circuit sample

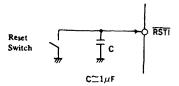

The reset signal applied to the RSTI terminal may be either the source voltage or can be generated with a capacitor connected to the RSTI terminal as shown below.

To reset the device, the RSTI signal should remain at "0" level for more than 20 times of the clock cycle when the source voltage has risen sufficiently and the clock signal is supplied.

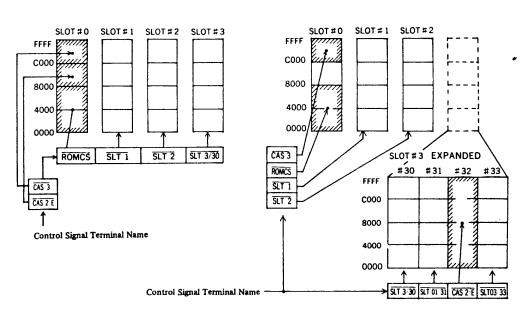

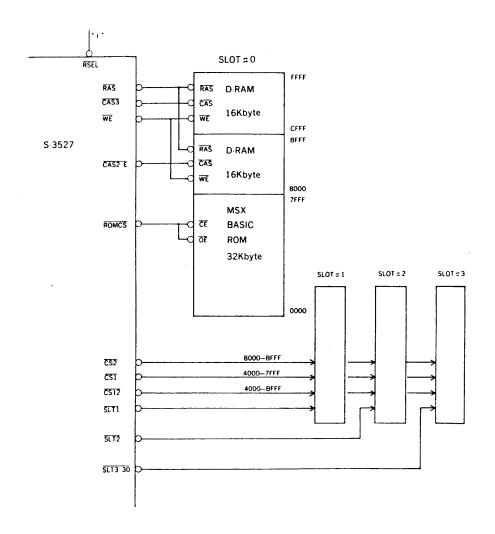

## Memory maps and expansion

#### (Slot # 3 is expanded)

## (Slot # 0 is expanded)

To expand a slot, it is necessary to supply the NAND of address signals A2, A8, A9, A10, A11, A12, and A13 (which are not supplied to the S-3527 normally) to the  $\overline{RSEL}$  terminal.

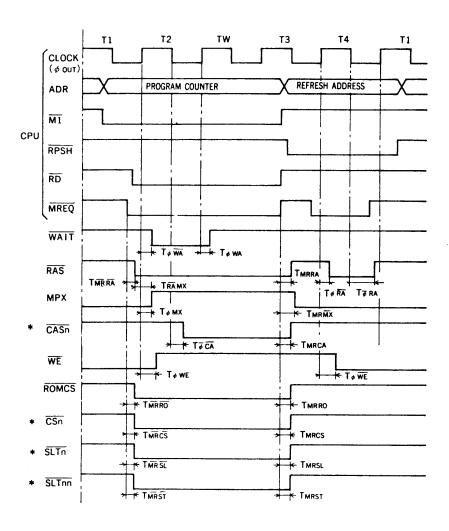

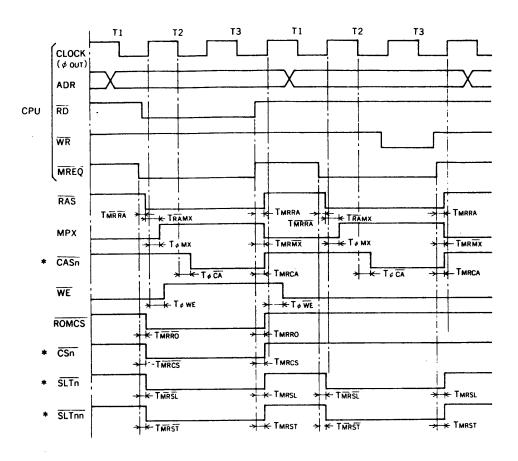

#### > Memory Control Signals

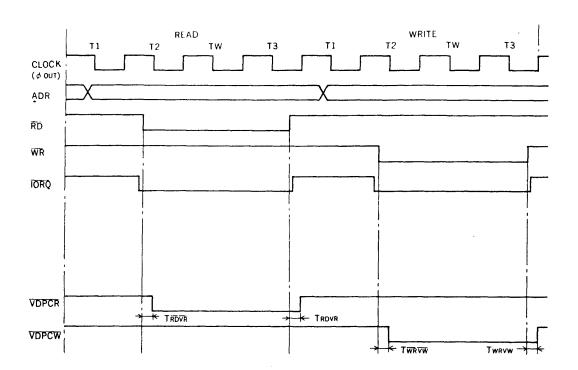

Refer to the timing diagrams given in the section of electrical characteristics for logic levels and timing of the system control signals ( $\overline{\text{MI}}$ , RFSH, MERQ,  $\overline{\text{IORQ}}$ , RD, and WR) coming from the CPU, memory control output signals ( $\overline{\text{ROMCS}}$ ,  $\overline{\text{RAS}}$ ,  $\overline{\text{MPX}}$ ,  $\overline{\text{CAS3}}$ ,  $\overline{\text{CAS2}}$ /E, WE,  $\overline{\text{CS1}}$ ,  $\overline{\text{CS2}}$ ,  $\overline{\text{CS12}}$ ,  $\overline{\text{SLT1}}$ ,  $\overline{\text{SLT2}}$ ,  $\overline{\text{SLT3}}$ /30,  $\overline{\text{SKT01}}$ /31, and  $\overline{\text{SLT03}}$ /33), CPU memory signal (WAIT), and VDP control signals ( $\overline{\text{VDPCR}}$  and  $\overline{\text{VDPCW}}$ ).

## >I/O Addresses and Functions

The functions of printer, VDP, SSG, general ports, keyboard, and slot select are fixed with I/O addresses given as shown below according to the MSX specifications.

#### I/O addresses and functions

| Function      | I/O ADR    | W/R | Description                               |

|---------------|------------|-----|-------------------------------------------|

|               | 90 (MKX)   | W   | Printer strobe out from PSTB (Bit 0)      |

| Printer       | 90         | R   | Printer status in to BUSY (Bit 1)         |

|               | 91         | w   | Print data out from PDB0 ~ 7 (Bits 0 ~ 7) |

|               | 98         | W   | VDP units timing signal out from VDPCW    |

| VDP           | 99         | W   | VDP write timing signal out from VDPCW    |

|               | 98         | R   | VDP read timing signal out from VDPCR     |

|               | 99         | R   | VDI Tead thining signal out from VDICK    |

| SSG and       | <b>A</b> 0 | W   | Address latch                             |

| general ports | Al         | w   | Data write                                |

| general ports | A2         | R   | Data read                                 |

|               | A8         | W   | Slot select signal register data write    |

|               | <b>A</b> 8 | R   | Slot select signal register data read     |

| Keyboard and  | <b>A</b> 9 | R   | Keyboard return signal read               |

| slot select   | AA         | w   | Keyboard drive signal register write      |

| •             | AA         | R   | Keyboard drive signal register read       |

|               | AB         | W   | Mode select                               |

# > Bit assignments of keyboard and slot select registers

| Function                   | Bit                                  | W/R                                     |                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                             |  |  |  |  |

|----------------------------|--------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Slot select register       | 0                                    |                                         | Select                                                                                                                                                                                                                                                                                                 | signal of 0000-3FFF slot                                                                                                                                                                                |  |  |  |  |

|                            | 2 3                                  | W/R                                     | Select signal of 4000-7FFF slot                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                         |  |  |  |  |

|                            | 5                                    | .,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, | Select signal of 8000-BFFF slot  Select signal of C000-FFFF slot                                                                                                                                                                                                                                       |                                                                                                                                                                                                         |  |  |  |  |

|                            | 6 7                                  |                                         |                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                         |  |  |  |  |

| Keyboard return            | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | R                                       | Keyboard return signal                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                         |  |  |  |  |

| Keyboard drive<br>register | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | W/R                                     | Keyboard drive signal (0 $\sim$ 10 decoded from the four bits are output to $\overline{Y0} \sim \overline{Y9}$ and $\overline{Y10} / \overline{SK}$ .)  Cassette tape control REM signal  Cassette tape write CMO signal $\overline{CAP}$ signal for CAPS lamp  Software-generated sound signal PPISND |                                                                                                                                                                                                         |  |  |  |  |

| Mode select                | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | w                                       | O When bit 7 is level "1", slot select and keyboard drive registers will be cleared. This is just like mode 0 of 8255A that ports PA and PC are assigned to output and port PB to input.  O O I                                                                                                        |                                                                                                                                                                                                         |  |  |  |  |

|                            | 0<br>1<br>2<br>3<br>4<br>5<br>6<br>7 | w                                       | Bo B1 B2 B3 O O O O                                                                                                                                                                                                                                                                                    | When bit 7 is level "0", each bit of keyboard drive registers can be set or reset.  B <sub>1</sub> ~ B <sub>3</sub> indicate bit No. Its content will be set when B <sub>0</sub> is 1 and reset when 0. |  |  |  |  |

#### > SSG and general ports

SSG is controlled by 14 registers (register contents can be read without affecting sounds). Sounds are generated with three 8-octave square wave generators, a pseudo-random noise generator, a a 5-bit envelope generator for single-shot and repeated attenuation, a sound level controller, a mixer of music sounds and noises, and a 5-bit D/A converter.

The general ports include an output port and an input port connected to registers.

## Register array

When high-order DB7 ~ DB4 of 8-bit address signal are 0 (H), low-order DB3 ~ DB0 (4 bits) select 15 registers. The address, once read, is retained, kept unaffected by data read/write, until a new address is given.

The register array is as follows.

## Register array

| Register       | Address<br>(H) | Bit Function                  | В                                            | B <sub>6</sub> | Bs      | B4         | Вз                         | B <sub>2</sub> | Bı       | Во   |

|----------------|----------------|-------------------------------|----------------------------------------------|----------------|---------|------------|----------------------------|----------------|----------|------|

| Ro             | 00             | Ci la f                       | 8-bit tone fine adjustment                   |                |         |            |                            |                |          |      |

| Rı             | 01             | Channel A frequency           |                                              | >              | $\leq$  |            | 4-bit t                    | one fin        | e adjust | ment |

| R <sub>2</sub> | 02             | Channel B fraguency           |                                              |                | 8-bit 1 | one fin    | e adjust                   | ment           |          |      |

| R3             | 03             | Channel B frequency           |                                              | $\geq$         | $\leq$  |            | 4-bit t                    | one fin        | e adjust | ment |

| R <sub>4</sub> | 04             | Channel C frequency           |                                              |                | 8-bit   | tone fin   | e adjust                   | ment           |          | 5    |

| Rs             | 05             | Chainles & frequency          |                                              |                |         |            | 4-bit tone fine adjustment |                |          |      |

| R <sub>6</sub> | 06             | Noise frequency               |                                              |                |         |            | 5-bit noise frequency      |                |          |      |

| R <sub>7</sub> | 07             | Sets mixer and general ports  |                                              |                | Noise   | Tone       |                            |                |          |      |

| K7             | 07             | Sets linker and general ports | "1"                                          | "0"            | С       | В          | A                          | С              | В        | A    |

| R <sub>8</sub> | 08             | Channel A sound level .       |                                              | ~              | $\leq$  | M          | L <sub>3</sub>             | L <sub>2</sub> | Lı       | Lo   |

| R9             | 09             | Channel B sound level         |                                              | ><             | $\leq$  | M          | La                         | L <sub>2</sub> | Lı       | Lo   |

| RA             | 0A             | Channel C sound level         |                                              | ><             | $\leq$  | M          | La                         | L <sub>2</sub> | Lı       | Lo   |

| Rв             | OB             | Envelope frequency            |                                              |                | 8-bit   | tone fir   | ne adjust                  | ment           |          |      |

| Rc             | 0C             | Envelope frequency            | 8-bit coarse                                 |                |         | adjustment |                            |                |          |      |

| RD             | 0D             | Envelope form                 |                                              |                |         | CONT       | ATT                        | ALT            | HOLD     |      |

| ><             | 0E             | Data of input port            | See the general port bit assignment table —— |                |         |            |                            |                |          |      |

| RF             | 0F             | Data of output port           |                                              | 500            | 80.110  |            | . Dit assignment table     |                |          |      |

<sup>\*</sup> Always keep the "port" bits of the register R7 at the levels shown above.

#### GENERAL PORTS

The input port has address 0E (H) and the output port 0F (H). They are controlled by an output port data latching register RF. The table at right shows relationships of bits and input/output terminals.

Relationships of bits and input/output terminals

| Port   | Bit                                           | i/o | Connecting terminal name                                                                                                                                                                    |

|--------|-----------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input  | B 0<br>B 1<br>B 2<br>B 3<br>B 4<br>B 5<br>B 6 | i   | F WD1 or FWD2 BACK1 or BACK2 LEFT1 or LEFT2 RIGHT1 or RIGHT2 TRGA1 or TRGA2 TRGB1 or TRGB2 JIS / 50 CMI  B6 of the output port selects FWD1 or FWD2. When B6 = "1", signal comes from FWD2. |

| Output | Bo<br>B1<br>B2<br>B3<br>B4<br>B5<br>B6        | O   | TRGA1 TRGB1 TRGA2 TRGB2 STB1 STB2 Input select of input port B0 ~ B5 (not delivered to outside)                                                                                             |

In initialized state, the terminals TRGA1, TRGB1, TRGA2, TRGB2 and STB2 are at "0" level; they go up to the prescribed level when the MSX BASIC is started. This being the case, the following explanation should be heeded when installing the MOUTH, which is to be connected to the general port. Attention is particularly necessary concerning the MSX MOUTH for setting the MOUTH mode at the time of turning on power supply.

In the initialization of the present device, mode A is selected in anticipation of any one of the above-indicated terminals going to "1" level. Mode B is selected by driving this level to "0" by operating a switch belonging to the MOUTH. Now, as mentioned above, no terminal goes to "1" level: this means that the MOUTH cannot be placed in mode A.

How to overcome this problematic situation follows:

- Connect the MOUTH when power supply is turned on for the MSX including the present device. If you already have the MOUTH connected before turning on power supply, disconnect it, turn on power supply and reconnect it. (The MOUTH will then automatically go into mode A.)

- By means of TRGA1 (TRGA2), set the mode of the MOUTH.

- Install such as a push-button switch in the power supply circuit from which the general port draws energy.

With the MOUTH installed as above, its mode can be set even when the MSX proper is in energized state (power supply ON). Such a MOUTH can be more conveniently made use of.

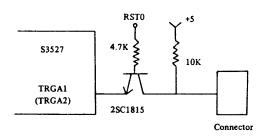

# $\bullet$ SETTING MUSIC SOUND FREQUENCIES (WITH REGISTERS $R_{0}\sim R_{s}$ )

Registers  $R_0 \sim R_s$  define the frequencies of square waves which music sound generators of channels A, B, and C produce.  $R_0$  and  $R_1$  define frequency of channel A,  $R_2$  and  $R_3$  of channel B,  $R_4$  and  $R_5$  of channel C. The contents TP (decimal) of a register define frequency FT as follows.  $F_{\phi}$  is the clock frequency.

$$F_T = \frac{F \phi}{32TP}$$

#### ■ SETTING NOISE FREQUENCY (WITH REGISTER R<sub>6</sub>)

The contents NP (decimal) of a register define the noise frequency FN as follows. F $\phi$  is the clock frequency.

$$F_N = \frac{F \phi}{32 N P}$$

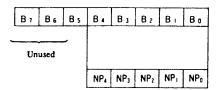

Noise Frequency Register R6

5-bit Value (NP) Defining Noise Frequency

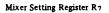

## ■ SETTING THE MIXER (WITH REGISTER R<sub>7</sub>)

The mixer mixes music sounds with noise according to bits  $B_5 \sim B_0$  of register  $R_7$ . "0" denotes that sound or noise be produced while "1" not. If "0" is designated for both sound and noise, they will appear mixed. If "0" is designated for sound or noise alone, it will appear unmixed. If "1" is designated for both sound and noise, none will be produced.

Always Set Just Like this

"0" Denotes that Sound or Noise be Produced

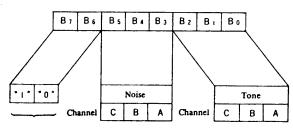

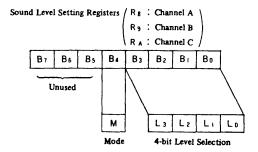

#### ■ SOUND LEVEL CONTROL (WITH REGISTERS R<sub>8</sub> ~ R<sub>A</sub>)

Registers  $R_8 \sim R_A$  control the sound levels of channels A, B, and C. M selects fixed sound level (M=0) or variable level (M=1). When M=0, one of 16 levels will be selected with a 4-bit signal  $L_3$   $L_2$   $L_1$   $L_0$ . To change sound level, vary  $L_3$   $L_2$   $L_1$   $L_0$ . When M=1, sound level is determined with a 5-bit signal  $E_4$   $E_3$   $E_2$   $E_1$   $E_0$  the built-in envelope generator generates.  $E_4$   $E_3$   $E_2$   $E_1$   $E_0$  varies with time.

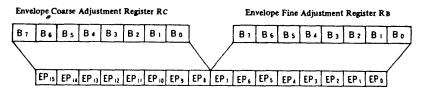

## ■ SETTING ENVELOPE FREQUENCY (WITH REGISTERS RB AND RC)

The envelope period data EP (decimal) determines the envelope repetition frequency FE as follows.  $F_{\phi}$  is the clock frequency.

$$F_E = \frac{F\phi}{512EP}$$

16-bit Envelope Period Data (EP)

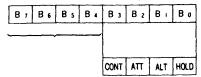

## ENVELOPE FORM CONTROL (WITH REGISTER RD)

The 5-bit signal  $E_4$   $E_3$   $E_2$   $E_1$   $E_0$  of the built-in envelope generator determines the envelope level. The envelope form is determined by incrementing or decrementing a counter of the envelope generator, stopping it every cycle, or repeating to do such things. Bits  $B_3 \sim B_0$  of register RD control the envelope form.

#### Envelope form control register RD

**Envelope Form Control Signals**

The envelope form varies as follows depending on CONT, ATT, ALT, and HOLD.

#### **Envelope forms**

| Вз   | B <sub>2</sub> | Βı  | Bo   | Favelone form                    |

|------|----------------|-----|------|----------------------------------|

| CONT | ATT            | ALT | HOLD | Envelope form                    |

| 0    | 0              | ×   | ×    |                                  |

| 0    | 1              | ×   | ×    |                                  |

| 1    | 0              | 0   | 0    |                                  |

| 1    | 0              | 0   | 1    |                                  |

| 1    | 0              | 1   | 0    |                                  |

| 1 1  | 9              | 1   | 1    |                                  |

| 1    | 1              | 0   | 0    |                                  |

| 1    | 1              | 0   | 1    |                                  |

| 1    | 1              | 1   | 0    |                                  |

| 1    | 1              | 1   | 1    |                                  |

|      |                |     | _    | 1 f = Envelope repetition period |

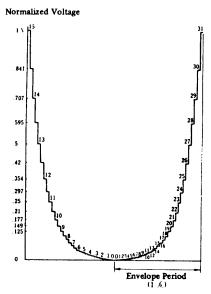

#### ■ D/A CONVERTER

The D/A converter produces output as shown below when the maximum amplitude is normalized to 1V. The logarithmic conversion provides a wide dynamic range and a natural feeling of attenuation.

Figure 1 Output level of the D/A converter The decimal values of sound level control signal L<sub>3</sub> L<sub>2</sub> L<sub>1</sub> L<sub>0</sub> are given along the left-side half of the curve and those of envelope counter output E<sub>4</sub> E<sub>3</sub> E<sub>2</sub> E<sub>1</sub> E<sub>0</sub> along the right-side half.

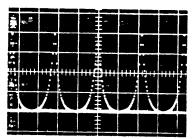

Figure 3 Waveform of three mixed sounds in fixed sound level (R.  $\sim$  R  $_{\lambda}$  =  $\times$   $\times$  × 01100)

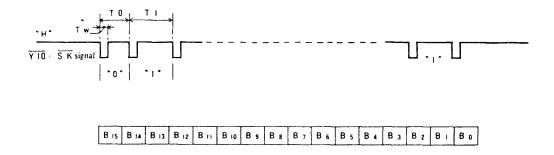

#### > Serial Key Input

If initialization has been performed to accept serial key input, serial data coming from the  $\overline{Y10}$  /  $\overline{SK}$  terminal according to the specifications given below can be ORed with key return signal.

Figure 1 Output level of the D/A converter

The serial signal coming to the  $\overline{Y10}/\overline{SK}$  terminal may be asynchronous to the clock. The waveform and timing should be as shown above. "0" is discriminated from "1" by the length of interval between negative pulses. In the above example, the input data are a series of "0", "1", ..., "1" from left to right. The data enters a 16-bit register (B<sub>15</sub>  $\sim$  B<sub>0</sub>). If more input signal follows, it enters bit B<sub>0</sub> of the register with the contents of B<sub>0</sub>  $\sim$  B<sub>14</sub> shifted to B<sub>1</sub>  $\sim$  B<sub>15</sub> one bit each and the old content of B<sub>15</sub> discarded.

Timing of serial signal

| Tilling of series against |             |            |  |  |  |  |

|---------------------------|-------------|------------|--|--|--|--|

| Symbol                    | MIN         | MAX        |  |  |  |  |

| T <sub>w</sub>            | 265<br>Fø   |            |  |  |  |  |

| То                        |             | 2040<br>Fø |  |  |  |  |

| Т 1                       | 2056<br>F Ø |            |  |  |  |  |

| T 0 - T w                 | 8<br>       |            |  |  |  |  |

Fφ: Clock frequency

After feeding in the serial input signal as above, set the contents ("Os" and "Is") of the keyboard drive register as shown in the bit allocation table, indicated below, which is for the keyboard and slot specifying register.

Select units of 8 bits each, as in the case of keyboard return signal, and read in the selected units to clear the 16-bit serial data register.

## Reading serial data and clearing register

| Keyboard drive bits |    | Description                                                                 |

|---------------------|----|-----------------------------------------------------------------------------|

| Во                  | Bı | Description                                                                 |

| 0                   | 0  | $B_0 \sim B_7$ Read from the same I/O address as of keyboard return signal. |

| 0                   | 1  | $B_8 \sim B_{15}$ $B_0$ and $B_8$ correspond to $X_0$ of keyboard return.   |

| 1                   | Χ. | Clears 16-bit register of serial data.                                      |

The 16-bit register will be cleared when  $B_0$  is set to 1. By setting  $B_1 \sim B_3$  appropriately, output can be delivered to any of the keyboard drive output terminals  $\overline{Y_1}$ ,  $\overline{Y_3}$ ,  $\overline{Y_3}$ ,  $\overline{Y_7}$ , and  $\overline{Y_9}$  just when the 16-bit register is cleared. The output signal can be sent out as the next serial data.

#### NOTES:

- 1) MSX does not support serial data.

- 2) If a serial data and a keyboard return signal come in to the CPU simultaneously, they will be ORed and read.

## Sample basic circuit (S-3527 and peripheral devices)

## Sample basic circuit (Memory control: expansion slot unused)

## Sample basic circuit (Memory control: RAM 64 Kbyte: expansion slot # 0 used)

\* The address bits which are not entered the S-3527 are NANDed and entered here.

## Sample basic circuit (Memory control: RAM 16K + 64 Kbyte: expansion slot #3 used)

<sup>\*</sup> The address bits which are not entered the S-3527 are NANDed and entered here.

#### • ELECTRICAL CHARACTERISTICS

#### 1. Absolute maximum ratings

| Parameter              | Rating                | Unit |

|------------------------|-----------------------|------|

| Supply voltage (VDD)   | -0.3 ~ 7.0            | V    |

| Input terminal voltage | $-0.3 \sim VDD + 0.3$ | v    |

| Ambient temperature    | 0~70                  | °C   |

| Storage temperature    | <b>−50 ~ 125</b>      | °c _ |

#### 2. Recommended operating conditions

| Parameter      | Symbol | Minimum | Typical | Maximum | Unit |

|----------------|--------|---------|---------|---------|------|

| Supply voltage | VDD    | 4.75    | 5.0     | 5.25    | V    |

|                | Vss    | 0       | 0       | 0       | v    |

## 3. DC characteristics (Top= 0°C $\sim$ 70°C, $V_{DD}$ =4.75 $v\sim$ 5.25v, $V_{SS}$ =0V, $V_{SS}$ =0V)

| Parameter              | Symbol | Condition                                                    | Minimum | Typical | Maximum | Unit |

|------------------------|--------|--------------------------------------------------------------|---------|---------|---------|------|

| Low input voltage      | VIL1   | (Except for $\overline{X_7} \sim \overline{X_0}$ )           | -0.3    |         | 0.8     | V    |

| •                      | VIL2   | $(\overline{X_7} \sim \overline{X_0})$                       | -0.3    |         | 1.5     | V    |

| High input voltage     | ViH1   | (Except for $\overline{X_1} \sim \overline{X_0}$ )           | 2.0     |         | VDD     | v    |

| 1                      | VIH2   | $(\overline{X_7} \sim \overline{X_0})$                       | 3.5     |         | VDD     | v    |

| Low output voltage     | Voli   | Nata Oli                                                     | 0       |         | 0.45    | v    |

|                        | VOL2   | Note O):<br>IOL = 10 mA (PSTB, WAIT,<br>Note O): CAPS, KANA) | 0       |         | 0.45    | v    |

| High output voltage    | Vон    | Note O): CAPS, KANA) IOH = 0.2 mA                            | 4.0     |         | VDD     | v    |

| Input current          | 11     | VIN- OV                                                      | -50     |         | -500    | μΑ   |

| Input leakage current  | ILI    | $VIN = 0 \sim 5V$                                            |         |         | 10      | μΑ   |

| Output leakage current | ILO    | $Vo = 0 \sim 5V$                                             |         |         | 10      | μΑ   |

| Supply current         | ldd    |                                                              |         |         | 35      | mA   |

Note O): IoL=1mA CMO,REM,PPiSND,VDPCR,VDPCW, \( \phi\)OUT, \( \bar{R}\)OMCS, \( \bar{R}\)A\$, \( \bar{R}\)S3, \( \bar{C}\)A\$3, \( \bar{C}\)A\$3,

$IOL = 2.4 \text{mA} \quad (\overline{DB0} \sim \overline{DB7}, \overline{SLT01/31}, \overline{SLT03/33}, \overline{CS1}, \overline{CS2}, \overline{CS12}, \overline{SLT2}, \overline{SLT3/30}, PDB0 \sim PDB7, \overline{RST0}, MPX)$

IOL=1.6mA (TRGA1,TRGA2,STB1,TRGA2,TRGB2,STB2) ..... Max.Vol = 0.5V

STB1, STB2

IOH = 0.2mA DB0 ~ DB7, ROMCS, MPX, RAS, CAS2/F, CAS3, WE, CS1, CS2, CS12, SLT1, SLT2, SLT3/30, SLT01/31, SLT03/33, VDPCR, VDPCW, PDB0 ~ PDB7, PSTB, CMO, REM, RSTO, PPISND,

#### 4. AC Characteristics (See Note 1.)

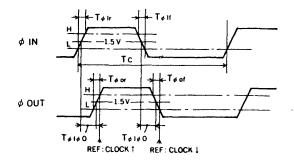

#### Clock timing

| Parameter                          | Symbol         | Condition            | Min. | Typical | Max. | Unit |

|------------------------------------|----------------|----------------------|------|---------|------|------|

| Clock period                       | Tc             |                      |      | 280     |      | ns   |

| Rise/decay times of clock (input)  | T # Ir. T # If |                      |      |         | 30   | ns   |

| Delay time of clock (input/output) | T#1,00         |                      |      | 13      |      | ns   |

| Rise/decay times of clock (output) | T ≠ or. T ∉ of | C <sub>L</sub> ≈70PF |      |         | 30   | ns   |

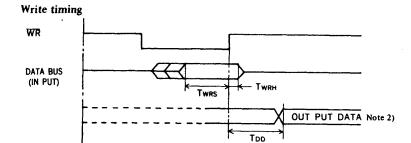

## Write timing

| Parameter             | Symbol   | Condition | Min. | Max. | Unit |

|-----------------------|----------|-----------|------|------|------|

| Data stable before WR | Twrs     |           | 300  |      | ns   |

| Data valid after WR   | Twrn     |           | 0    |      | ns   |

| Output data delay     | $T_{DD}$ | Note 2)   |      | 250  | ns   |

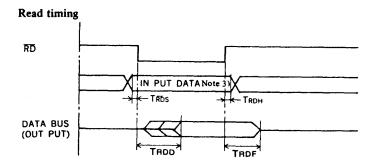

## Read timing

| Parameter             | Symbol | Condition | Min. | Max. | Unit |

|-----------------------|--------|-----------|------|------|------|

| Data delay            | TRDD   |           | 1    | 250  | ns   |

| Time to data floating | TRDF   |           | l    | 100  | ns   |

| Data stable before RD | TRDS   | )         | 0    |      | ns   |

| Data valid after RD   | Tron   | Note 3)   | 0    |      | ns   |

#### Notes:

- 1) The address and data buses and control signal lines are assumed to be connected directly to the CPU.

- 2) Applies to  $\overline{Y_0} \sim \overline{Y_{10}}$ , STBI, STB, TRGAI, TRGA2, TRGBI, TRGB2,  $\overline{CAPS}$ ,  $\overline{KANA}$ , REM, and CMO.

- 3) Applies to  $\overline{X_0} \sim \overline{X_7}$ , FWD1, FWD2, BACK1, BACK2, LEFT1, LEFT2, RIGHT1, RIGHT2, TRGA1, TRGA2, TRGB1, TRGB2, CMI, and JIS/50.

M1 cycle, memory read/write cycle, and I/O cycle timing

| Paramete                                                  | r            | Symbol | Condition                      | Min. | Max. | Unit |

|-----------------------------------------------------------|--------------|--------|--------------------------------|------|------|------|

| CLOCK 1 WAIT                                              | ↓ Delay time | Tø WA  | C <sub>L</sub> =70PF           |      | 60   | ns   |

| CLOCK T WAIT                                              | † "          | To WA  | $C_L = 70 PF R_L = 680 \Omega$ |      | 60   | ns   |

| MREQ ↓ - RAS                                              | <b>1</b> "   | TMRRA  | $C_L = 100PF$                  |      | 60   | ns   |

| $\overline{\text{MREQ}} \uparrow - \overline{\text{RAS}}$ | <b>†</b> "   | TMRRA  | "                              |      | 70   | ns   |

| CLOCK † - RAS                                             | 1 "          | TøRA   | " •                            |      | 70   | ns   |

| CLOCK † – RAS                                             | <b>†</b> "   | Tora   | ,,                             | 90   | 180  | ns   |

| CLOCK † MPX                                               | 1 "          | T ø MX | "                              |      | 70   | ns   |

| MREQ 1 - MPX                                              | 1 "          | TMRMX  | "                              |      | 70   | ns   |

| RAS ↓ MPX                                                 | 1 "          | TRAMX  | , "                            | 50   | j    | ns   |

| CLOCK ↑ -* CASn                                           | 1 "          | TøCA   | "                              |      | 70   | ns   |

| MREQ † -*CASn                                             | <b>†</b> "   | TMRCA  | "                              |      | 70   | ns   |

| CLOCK † - WE                                              | † "          | T & WE | "                              | 30   | 70   | ns   |

| CLOCK † – WE                                              | <b>1</b> "   | T ø WE | "                              | 30   | 70   | ns   |

| MREQ   ROMCS                                              | 1 "          | TMRRO  | "                              |      | 70   | ns   |

| MREQ 1 - ROMCS                                            | † "          | TMRRO  | "                              |      | 70   | ns   |

| MREQ ↓ -*CSn                                              | 1 "          | TMRCS  | "                              |      | 60   | ns   |

| MREQ ↑ -* CSn                                             | † "          | TMRCS  | "                              |      | 70   | ns   |

| $\overline{MREQ} \downarrow - \overline{SLTn}$            | ļ "          | TMRSE  | "                              |      | 60   | ns   |

| MREQ † -*SLTn                                             | † "          | TMRSL  | "                              |      | 70   | ns   |

| MREQ   -*SLTnn                                            | ļ "          | TMRST  | "                              | !    | 70   | ns   |

| MREQ † -*SLTnn                                            | † "          | TMRST  | "                              |      | 70   | ns   |

| $\overline{RD}$ $\downarrow - \overline{VDPCR}$           | <b>1</b> "   | TROVR  | "                              |      | 70   | ns   |

| $\overline{RD}$ $\uparrow - \overline{VDPCR}$             | <b>†</b> "   | TROVE  | "                              |      | 70   | ns   |

| WR ↓ - VDPCW                                              | 'l "         | TWRVW  | "                              | !    | 70   | ns   |

| $\overline{WR}$ † – $\overline{VDPCW}$                    | †† "         | Twrvw  | ,,                             |      | 50   | ns   |

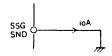

## Analog output (SSG SND)

| Parameter              | Symbol | Condition | Min.  | Typical | Max. | Unit |

|------------------------|--------|-----------|-------|---------|------|------|

| Maximum output current | IOA    | See below | (0.8) | (1.2)   | 1.7  | mApp |

## Clock timing

|                 | *H*     | *L*    |

|-----------------|---------|--------|

| CLOCK(\$ OUT)   | VDD0.6V | 0.45V  |

| OUT PUT         | 2.0V    | V8.0   |

| IN PUT or of IN | 2.0V    | 0.8V   |

| FLOAT           | Δ٧      | ± 0.5V |

|                 |         |        |

## M1 cycle timing

Note 4): The signal names marked with \* are detailed below.

$\begin{array}{lll} \hline CASn & : CAS \, 2/E, \, CAS \, 3 \\ \hline CSn & : CS1, \, CS \, 2, \, CS12 \\ \hline SLTn & : SLT1, \, SLT2, \, SLT \, 3/30 \\ \hline SLTnn & : SLT01/31, \, SLT03 \, 33 \\ \hline \end{array}$

## Memory read/write timing

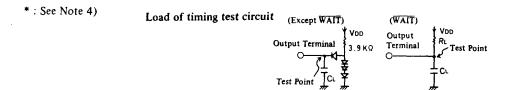

\* : See Note 4)

# I/O cycle timing

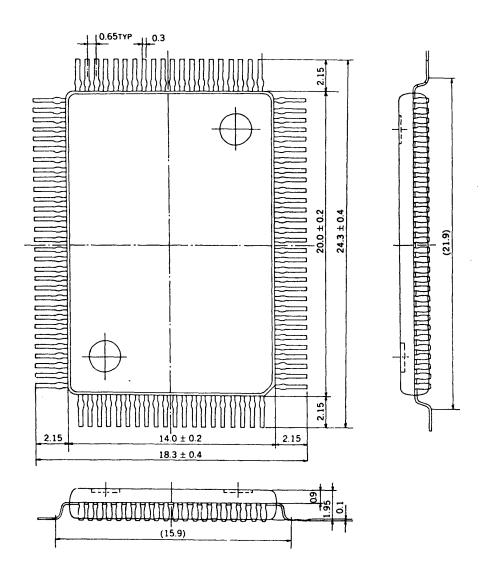

## **EXTERNAL DIMENSIONS DIAGRAM**

## > Precautions for Use

The S-3527 is a CMOS device and its input terminals will be directly connected to the outside. When using it, protect it from latch-up and static electricity.

Latch-up is likely to happen in the following cases.

- A signal line is connected to the S-3527 from a separate system to which power is supplied separately from the S-3527, and the S-3527's power is later to rise than the other's.

- A surge voltage rises when power has turned on.

- The supply voltage of the S-3527 exceeds the rated range.

- The resistance of the power lines connected to the S-3527 is not low.

- A separate system has been connected to an input/output terminal while the S-3527 is operating

- Someone has touched an input/output terminal by part of his body like hand while the S-3527 is operating.