Инструменты пользователя

7. Технические характеристики

Содержание

7.1.Схемы входных и выходных каскадов

На приведенных ниже схемах приняты следующие обозначения:

- I (INPUT) — внешний вход;

- O (OUTPUT)— внешний выход;

- i (input) — внутренний вход;

- o (output) — внутренний выход;

- I/О (INPUT/OUTPUT) — внешний вход/выход;

- HOLD — внутренний сигнал перевода в третье состояние

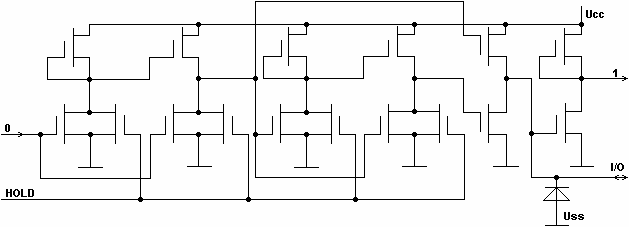

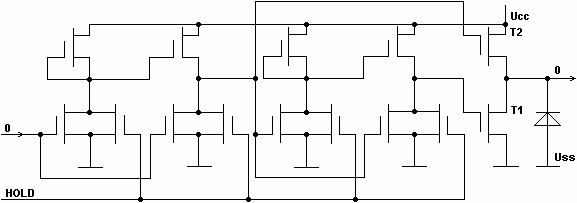

Рис. 7.1. Схема входов /WAIT, /INT, /NMI, /RESET, /BUSRQ и C.

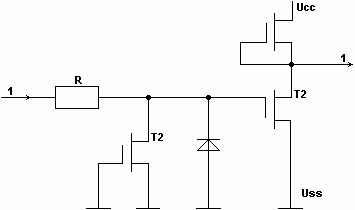

Рис. 7.2. Схема выходов /M1, /RFSH, /HALT и /BUSAK.

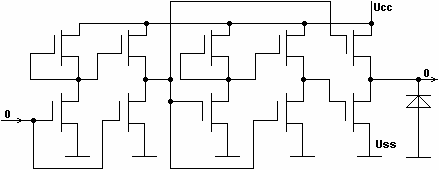

Рис. 7.3. Схема тристабильных выходов A0–A15, /MREQ, /IORQ, /RD и /WR.

7.2. Электрические и временные параметры.

7.2.1. Статические характеристики.

Все напряжения даны относительно U SS =0 В.

| Параметр | Обозначение | Единица измерения | Минимальное значение | Максимальное значение | Пояснения |

|---|---|---|---|---|---|

| Рабочее напряжение | UCC | В | 4,75 | 5,25 | при V m =0÷70°C |

| Входное напряжение | UIL | В | -0,3 | 0,6 | |

| UIH | В | 2 | UCC | ||

| Входное напряжение тактового сигнала | UILC | В | -0,3 | 0,45 | |

| UIHC | В | UCC -0,6 | UCC +0,3 | ||

| Выходное напряжение | UOL | В | - | 0,4 | при IOL=1,8мA Vm=0÷70°C при IOH=-0,25мA Vm=0÷70°C |

| Потребление тока | ICC | мА | - | 150/2001) | при UCC =5B±5% и Vm=0÷70°C |

| Входной ток утечки | ILI | мкА | - | 10 | при UI=0+U CC |

| Ток утечки трёхстабильного выхода в высокоомном состоянии | ILO | мкА | - | 10 | при UO=0+UCC |

| Ток утечки шины данных при вводе | ILD | мкА | - | 10 | UI=0+UCC |

| Входная ёмкость тактовой линии | CC | пФ | - | 35 | при Vm=25°C и f=1МГц |

| Входная ёмкость | CI | пФ | - | 5 | |

| Выходная ёмкость | CO | пФ | - | 10 | |

7.2.2. Динамические характеристики Z80

При UCC=5B±5%, CL=50 пФ и Vm=0÷70°C.

| Параметр | Обозначение | Минимальное значение (нс) | Максимальное значение (нс) |

|---|---|---|---|

| Период тактовых импульсов | tC | 400 | 2) |

| Длительность низкого уровня тактового сигнала | tW(CL) | 180 | 2000 |

| Длительность высокого уровня тактового сигнала | tW(CH) | 180 | 3) |

| Длительность переднего/заднего фронта тактового сигнала | tr , tf | - | 30 |

| Установка сигнала /WAIT до H-L перехода такта | tа(WT) | 70 | - |

| Установка сигнала /RESET до L-H перехода такта | tа(RS) | 90 | - |

| Установка сигнала /INT до L-H перехода такта | tа(IT) | 60 | - |

| Установка сигнала /BUSRQ до L-H перехода такта | tа(BQ) | 80 | - |

| Установка данных до L-H перехода такта в цикле M1 | tа(D) | 50 | - |

| Установка данных до H-L перехода такта в циклах M2–M5 | tac(D) | 60 | - |

| Задержка сигналов на шинах | tH | 0 | - |

| Ширина импульса низкого уровня сигнала /NMI | tW(NMI) | 80 | - |

Времена задержек

При UCC=5B±5%, CL=50 пФ и Vm=0÷70oC.

| Задержка | Обозначение | Максимальное значение (нс) |

|---|---|---|

| от H-L перехода такта до /M1=L | tDL(M1) | 130 |

| от H-L перехода такта до /M1=H | tDH(M1) | 130 |

| от H-L перехода такта до /MREQ=H | tDHC(MR) | 100 |

| от L-H перехода такта до /MREQ=H | tDHC̅(MR) | 100 |

| от H-L перехода такта до /MREQ=L | tDHC̅(MR) | 100 |

| от L-H перехода такта до /IORQ=L | tDLC(IR) | 90 |

| от H-L перехода такта до /IORQ=L | tDLC̅(IR) | 110 |

| от L-Н перехода такта до /IORQ=H | tDHC(IR) | 100 |

| от H-L перехода такта до /IORQ=H | tDHC̅(IR) | 110 |

| от L-H перехода такта до /RD=L | tDLC(RD) | 100 |

| от H-L перехода такта до /RD=L | tDLC̅(RD) | 130 |

| от L-H перехода такта до /RD=H | tDHC(RD) | 100 |

| от H-L перехода такта до /RD=H | tDHC̅(RD) | 110 |

| от L-H перехода такта до /WR=L | tDLC(WR) | 80 |

| от H-L перехода такта до /WR=L | tDLC̅(WR) | 90 |

| от L-H перехода такта до /WR=H | tDHC̅(WR) | 100 |

| от L-H перехода такта до /RFSH=H | tDH(RF) | 150 |

| от L-H перехода такта до /RFSH=L | tDL(RF) | 180 |

| от H-L перехода такта до /HALT=L | tD(HT) | 300 |

| от L-H перехода тахта до /BUSAK=L | tDL(BA) | 120 |

| от H-L перехода такта до /BUSAK=H | tDH(BA) | 110 |

| вывода адреса | tD(AD) | 145 |

| адреса до перехода к третьему состоянию | tF(AD) | 110 |

| вывода данных | tD(D) | 230 |

| данных до перехода к третьему состоянию в цикле записи | tF(D) | 90 |

| сигналов /MREQ, /IORQ, /RD, /WR до перехода к третьему состоянию | tF(C) | 100 |

Время задержки увеличивается на 10 нс при возрастании ёмкости нагрузки на каждые 50 пФ до максимально 200 пФ для шины данных и 100 пФ для шин адреса и управления.

Дополнительные данные о времени.

| Вывод адреса до активизации /MREQ в циклах обращения к памяти | tacm= tw(CH) + tF - 75 нс |

| Вывод адреса до активизации /IORQ, /RD или /WR в циклах ввода/вывода | tac1 = tC – 80 нс |

| Задержка адреса после снятия /RD или WR | tca = tw(CL) + tr - 40 нс |

| Задержка адреса после снятия /RD или /WR при переходе в третье состояние | tcaf = tw(CL) + tr - 60 нс |

| Вывод данных до активизации /WR в циклах обращения к памяти | tdcm = tC - 210нС |

| Вывод данных до активизации /WR в циклах ввода–вывода | tac1 = tw(CL) + tr - 210 нс |

| Задержка данных после снятия /WR | tcdf= tw(CL) + tr - 60 нс |

| Ширина импульса низкого уровня /MREQ | tw(MRL) = tC - 40 нс |

| Ширина импульса высокого уровня /MREQ | tw(MRH) = tw(CH) + tF - 30 нс |

| Ширина импульса низкого уровня /WR | tw(WRL) = tC - 40 нс |

| Вывод /M1 до активизации /IORQ в цикле подтверждения прерывания | tM1 = 2tC + tw(CH) +tF - 80 нс |

7.2.3. Динамические характеристики Z80A

При UCC=5B±5%, CL=50пФ и Vm=0÷70°C.

| Параметр | Обозначение | Минимальное значение (нс) | Максимальное значение (нс) |

|---|---|---|---|

| Период тактовых импульсов | tC | 250 | 4) |

| Длительность низкого уровня тактового сигнала | tW(CL) | 110 | 2000 |

| Длительность высокого уровня тактового сигнала | tW(CH) | 110 | 5) |

| Длительность переднего/заднего фронта тактового сигнала | tr , tf | - | 30 |

| Установка сигнала /WAIT до H-L перехода такта | tа(WT) | 70 | - |

| Установка сигнала /RESET до L-H перехода такта | tа(RS) | 60 | - |

| Установка сигнала /INT до L-H перехода такта | tа(IT) | 80 | - |

| Установка сигнала /BUSRQ до L-H перехода такта | tа(BQ) | 50 | - |

| Установка данных до L-H перехода такта в цикле M1 | tаc(D) | 35 | - |

| Установка данных до H-L перехода такта в циклах M2-M5 | tac(D) | 50 | - |

| Задержка сигналов на шинах | tH | 0 | - |

| Ширина импульса низкого уровня сигнала /NMI | tW(NMI) | 80 | - |

Времена задержек

При UCC=5B±5%, CL=50 пФ и Vm=0÷70°C.

| Задержка | Обозначение | Максимальное значение (нс) |

|---|---|---|

| от H-L перехода такта до /M1=L | tDL(M1) | 100 |

| от H-L перехода такта до /M1=H | tDH(M1) | 100 |

| от H-L перехода такта до /MREQ=H | tDHC(MR) | 85 |

| от L-H перехода такта до /MREQ=H | tDHC̅(MR) | 85 |

| от H-L перехода такта до /MREQ=L | tDHC̅(MR) | 85 |

| от L-H перехода такта до /IORQ=L | tDLC(IR) | 75 |

| от H-L перехода такта до /IORQ=L | tDLC̅(IR) | 85 |

| от L-Н перехода такта до /IORQ=H | tDHC(IR) | 85 |

| от H-L перехода такта до /IORQ=H | tDHC̅(IR) | 85 |

| от L-H перехода такта до /RD=L | tDLC(RD) | 85 |

| от H-L перехода такта до /RD=L | tDLC̅(RD) | 95 |

| от L-H перехода такта до /RD=H | tDHC(RD) | 85 |

| от H-L перехода такта до /RD=H | tDHC̅(RD) | 85 |

| от L-H перехода такта до /WR=L | tDLC(WR) | 65 |

| от H-L перехода такта до /WR=L | tDLC̅(WR) | 80 |

| от L-H перехода такта до /WR=H | tDHC̅(WR) | 80 |

| от L-H перехода такта до /RFSH=H | tDH(RF) | 120 |

| от L-H перехода такта до /RFSH=L | tDL(RF) | 130 |

| от H-L перехода такта до /HALT=L | tD(HT) | 300 |

| от L-H перехода тахта до /BUSAK=L | tDL(BA) | 100 |

| от H-L перехода такта до /BUSAK=H | tDH(BA) | 100 |

| вывода адреса | tD(AD) | 110 |

| адреса до перехода к третьему состоянию | tF(AD) | 90 |

| вывода данных | tD(D) | 150 |

| данных до перехода к третьему состоянию в цикле записи | tF(D) | 90 |

| сигналов /MREQ, /IORQ, /RD, /WR до перехода к третьему состоянию | tF(C) | 80 |

Время задержки увеличивается на 10 нс при возрастании ёмкости нагрузки на каждые 50 пФ до максимально 200 пФ для шины данных и 100 пФ для шин адреса и управления.

Дополнительные данные о времени

| Вывод адреса до активизации /MREQ в циклах обращения к памяти | tacm = tw(CH) + tF - 65 нс |

| Вывод адреса до активизации /IORQ, /RD или /WR в циклах ввода/вывода | tac1 = tC - 70 нс |

| Задержка адреса после снятия /RD или WR | tca = tw(CL) + tr - 50 нс |

| Задержка адреса после снятия /RD или /WR при переходе в третье состояние | tcaf = tw(CL) + tr - 45 нс |

| Вывод данных до активизации /WR в циклах обращения к памяти | tdcm = tC - 170 нс |

| Вывод данных до активизации /WR в циклах ввода–вывода | tac1 = tw(CL) + tr - 170 нс |

| Задержка данных после снятия /WR | tcdf = tw(CL) + tr - 70 нс |

| Ширина импульса низкого уровня /MREQ | tw(MRL) = tC - 30 нс |

| Ширина импульса высокого уровня /MREQ | tw(MRH) = tw(CH) + tF - 20 нс |

| Ширина импульса низкого уровня /WR | tw(WRL) = tC - 30 нс |

| Вывод /M1 до активизации /IORQ в цикле подтверждения прерывания | tM1 = 2tC + tw(CH) +tF - 65 нс |

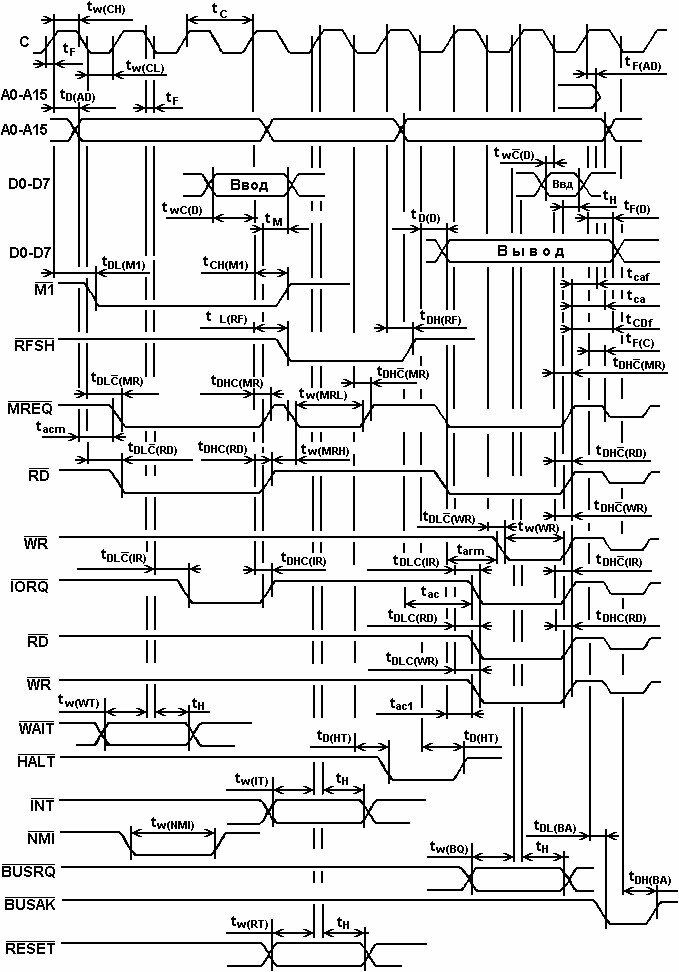

Рис. 7.5. Временные характеристики МП Z80/Z80A (к 7.2.2 и 7.2.3)

7.2.4. Предельные значения

Предельные значения даны при Va =0÷70°C.

| Параметр | Обозначение | Единица измерения | Минимальное значение (нс) | Максимальное значение (нс) |

|---|---|---|---|---|

| Рабочее напряжение | UCC | В | -0,3 | 7 |

| Входное напряжение | UI | В | -0,3 | 7 |

| Диапазон рабочей температуры | Va | °C | 0 | 70 |

| Диапазон температуры хранения | Vatu | °C | -65 | 150 |

| Мощность рассеяния | P | Вт | - | 1,5 |

Существует несколько исполнений (указывается на корпусе):

| C | керамический корпус |

| P | пластмассовый корпус |

| S | стандартные условия эксплуатации (5В±5%, 0÷70°C) |

| E | расширенные условия эксплуатации (5В±5%, -40÷85°С) |

| M | военное исполнение (5В±10%, -55÷125°С) |

7.3. Надежность

Интенсивность отказов:

LPO,В < 5×10-5 ч-1

При средней электрической нагрузке (рабочее напряжение UCC от 4,75 В до 5,25 В и температуре окружающей среды Va < 50°С, нормальной климатической и механической нагрузке наработка на отказ 2 000 000 часов.